00 01 11 10

00 01 11 10

III

## PHY 233 Quiz II

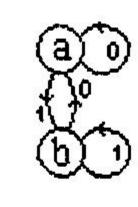

In the state transition diagram R, S, and T are outputs.

- What are the priorities (rules) in the state assignment maps I? (8 pts.)

- What are the priorities (rules) in the state assignment maps II? (6 pts.)

Can you suggest an assignment (III) that avoids the Bonus:

violations in I & II? Justify your answer briefly

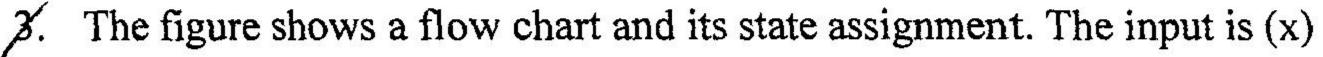

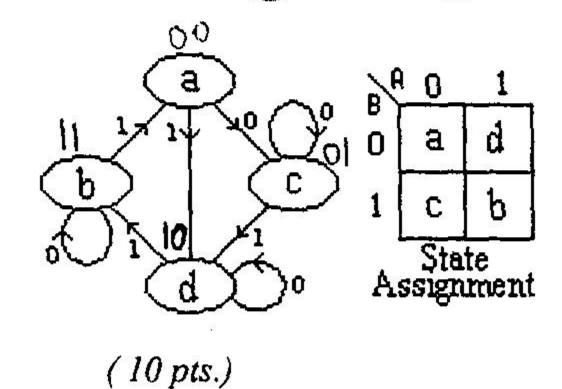

For the state transition diagram shown

Reduce the number of states by the method of grouping.

(12 pts.)

Draw the reduced state transition diagram.

(5 pts.)

Prepare the present state-next state charts

(3 pts.)

26. Prepare the Karnaugh Maps for D<sub>A</sub> and D<sub>B</sub>

(6 pts.)

Convert the D<sub>B</sub> map to JK maps

(6 pts.)

Realize the circuit of Q3 by D Flip Flops and Mux implementation. You will be graded on the basis of consistency with your answer for part (b)

Answer 5 of the following 8 questions briefly:

- How many 16x4Bit memory chips (our own 74189) are needed to construct a 1Kbyte memory? How do registers help to remove glitches at the output? whit we with low

What is the advantage in using a One-Hot state Machine? What is the price paid?

- What are the disadvantages of Mux realizations of ASM's?\

- What is(are) the advantage(s) of state reduction?

- Why isn't any Johnson counter self correcting?

- How many distinct state assignments will there be if we use a 2-bit address for the ASM shown? Justify your answer explicitly showing the state assignment map(s)

Good Luck!

14 + 17 + 15 + 10 + 30 = 100