# Question 1. (7 points)

|              | T= True;                    | F = F            | alse      |              | & N.               | O.A = None Of the Above |

|--------------|-----------------------------|------------------|-----------|--------------|--------------------|-------------------------|

|              | 37 - 27 - 32 - 32 - 32 - 32 |                  |           |              |                    |                         |

| 1- A         | register is mainl           | ly used for shir | fting an  | d storing d  | ata                |                         |

|              | a) F                        | b) T             |           |              |                    |                         |

|              | ROM can be vie              |                  | rammat    | ole AND/C    | R array in which   | the AND plane is        |

|              | a) F                        | b) T             |           |              |                    |                         |

| 3- As<br>S=0 |                             | ctive LOW SR     | flip-flo  | op is used;  | the output Q is ea | qual to 0 when R=1 and  |

|              | a) F                        | b) T             |           |              |                    |                         |

| 4- Ho        | ow many flip-flo            | ops are require  | d to cou  | int up to 10 | 0010               |                         |

|              | a) 7                        | b) 10            | c) 5      | d) 20        | e) N.O.A           |                         |

|              | e output in Mea<br>curred.  | ly Machine is    | change    | d only whe   | en the clock edge- | triggering has          |

|              | a) F                        | b) T             |           |              |                    |                         |

|              | a 50 MHz frequi             |                  |           | input CLO    | CK of a JK flip-f  | lop with J=K=1, what    |

|              | a) 50 MHz                   | b) 25MHz         | c) 12     | .5 MHz       | d) 100 MH          | Iz e) N.O.A             |

| 7- Se        | quential circuits           | contain memo     | ory and   | combinati    | onal circuits do n | ot.                     |

|              | a) F                        | b) T             |           |              |                    |                         |

| 8- W         | nen a I-K flin-flo          | on is construct  | ed from   | SR flin-fl   | on which one of    | the following is true?  |

|              | a) S= J.Q and               |                  | 04 110111 |              | and R= K + Q'      | alle following to tree. |

|              | c) S= J.Q and               | and the second   |           |              | Q' and R= K.Q      | e) N O A                |

|              |                             | ,                | •         |              | e und it ind       | 0,1110.11               |

| y- An        | asynchronous                |                  | need a    | CLOCK        |                    |                         |

|              | a) F                        | b) T             |           |              |                    |                         |

| 10- A        | J-K flip-flop is            | implemented      | using o   | nly          |                    |                         |

|              | a) AND gates                | b) OF            | ₹ gates   | C            | ) NAND gates       | d) NOR gates            |

|              |                             |                  |           |              |                    |                         |

|              |                             |                  |           |              |                    |                         |

Final

## Question 2. (7 points)

Design a combinational circuit that can realize the following algorithm, using only (two or three) 2:1 Multiplexers, two Full Adders, and two inverters; VCC (5 V) and GND (0V) can be used in this design.

```

Begin (algo.)

IF Sel = I then

Out = A+B

Else

Out = A-B

End (Algo.)

```

Note: A, B and Out are 2 bits each.

3/8

## Question 3. (7 points)

A certain country is ruled by family of four members, A, B, C and D. A has 25 votes, B has 40 votes C has 15 votes and D has 10 votes. Any decision taken by the family is based on its receiving at least 60% of the total number of votes. Design a combinational circuit that will produce on output of 1 if a certain motion is approved by the family.

|   | In | Output |    |                 |

|---|----|--------|----|-----------------|

| A | В  | C      | D  | Decision        |

|   |    |        | ., | - (1 <u>2</u> 4 |

|   |    |        |    |                 |

| _ |    |        |    |                 |

|   |    |        |    |                 |

|   |    |        |    |                 |

|   |    |        |    |                 |

|   |    |        |    |                 |

|   |    |        |    |                 |

|   |    |        |    |                 |

4/8 A.Kassem

#### Question 4. (7 points)

Show how to modify the internal circuit of the shift register (seen in class and home work), to load, or rotate left/right according to the following table.

Hint: This shift register is composed of 4 MUXs and 4 D Flip-Flops.

| Input |   |     | Next | State | Action |              |

|-------|---|-----|------|-------|--------|--------------|

| Α     | В | Q3+ | Q2+  | QI+   | Q0+    | 8            |

| 0     | 0 | Q3  | Q2   | Q1    | Q0     | No change    |

| 0     | 1 | Q0  | Q3   | Q2    | Q1     | Rotate Right |

| 1     | 0 | Q2  | Q1   | Q0    | Q3     | Rotate left  |

| 1     | 1 | D3  | D2   | D1    | D0     | Load         |

## Question 5. (7 points)

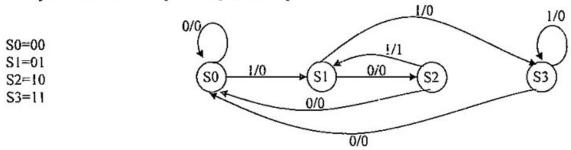

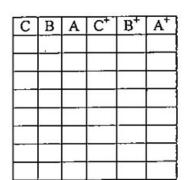

Referring to following state diagram, construct the state table and design the circuit using D flip-flops. Is it a Moore or Mealy machine? What does this design detect?

Hint: find the next state expression for each input.

į

## Question 6 (7 points)

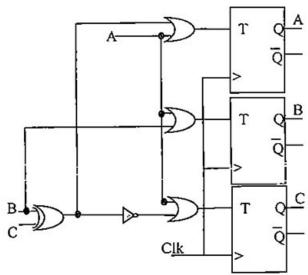

Draw the sequence(s) of the following circuit (counter). Assume that T flip-flops are rising edge-triggered and that all flip-flops are initially cleared and have delays. Show all calculations to receive full credits.

Use k-map if needed

|    | 0 | 1     |

|----|---|-------|

| 00 |   |       |

| 01 |   | (4)40 |

| 11 |   |       |

| 10 |   |       |

| 1  | 0 | 1 |

|----|---|---|

| 00 |   |   |

| 10 |   |   |

| H  |   |   |

| 10 |   |   |

| 1  | 0 | 1 |

|----|---|---|

| 00 |   |   |

| 01 |   |   |

| 11 |   |   |

| 10 |   |   |

| \  | 0 | 1 |

|----|---|---|

| 00 |   |   |

| 01 |   |   |

| 11 |   |   |

| 10 |   |   |

#### Bonus. (4 points)

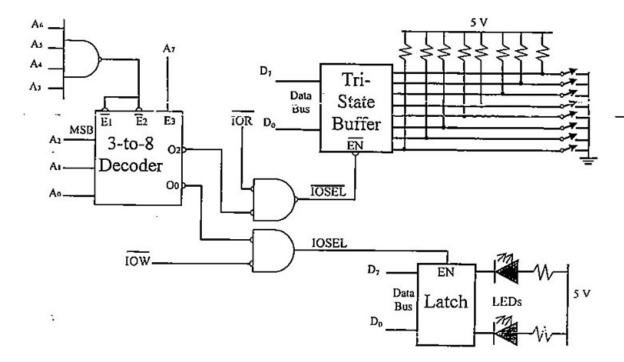

Find, when the inputs enable (EN) is ON of Tri-State Buffer and Latch? What does the following system do?

Hint: 3:8 Decoder is enable when E1=E2=0 and E3=1.

>

3:8 Decoder is an active low, example O1=0 when A2=A1=A0=0; and O3=O2=O1=1

IOW: Input/Output Write IOW: Input/Output Read